Long description

Back

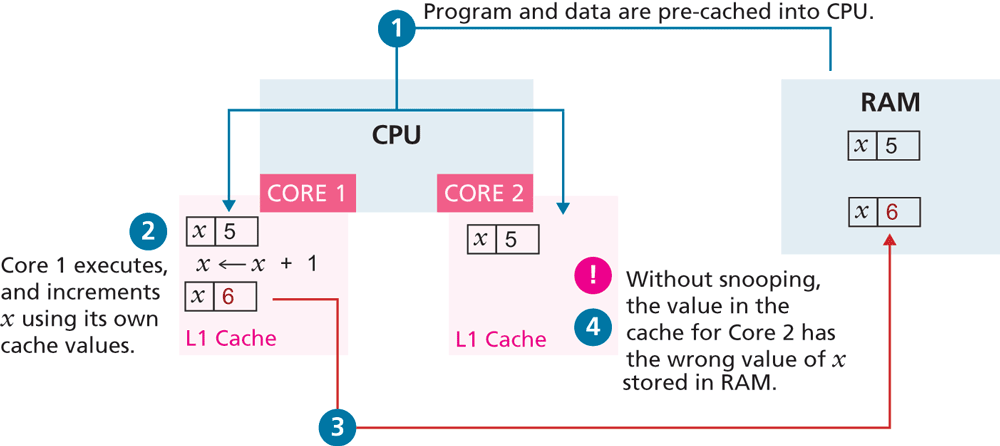

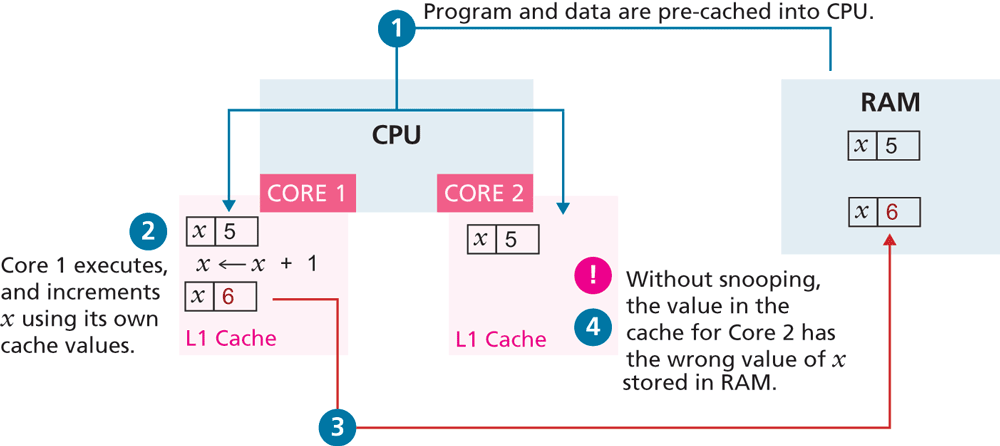

The figure shows a C P U with two core processors: Core 1 and Core 2.

Step 1: Program and data are pre-cached into the C P U.

Both the core processors have L 1 cache and the initial value of x is 5. It also shows a RAM block with value of x as 5.

Step 2: The core 1 processor executes, and increments x using its own cache values. This updates x to x plus 1, which in turn updates the value of x to 6. The Core 1 processor updates the value of x to 6 in the RAM.

Note: Without snooping, the value in the cache for Core processor 2 has the wrong value of x stored in RAM.

Back